### **Features and Benefits**

- Wide input voltage range: 8 to 50 V

- Integrated low R<sub>DS(on)</sub> DMOS switch

- 3 A continuous output current

- Adjustable fixed off-time

- Highly efficient

- Adjustable output: 0.8 to 24 V

- Small package with exposed thermal pad

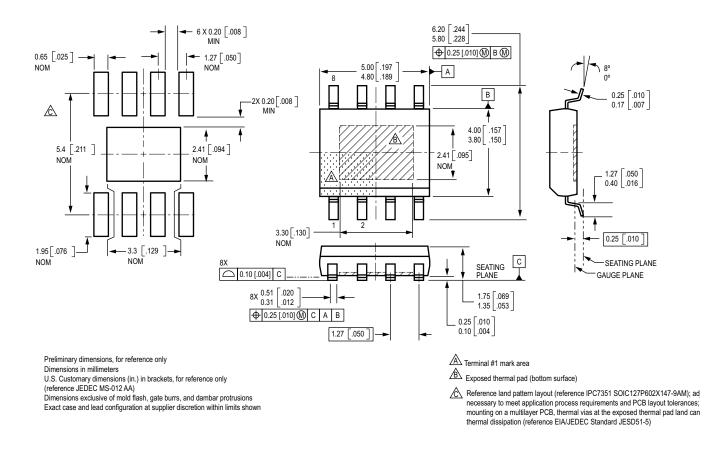

# Package: 8 pin SOIC with exposed thermal pad (suffix LJ)

Approximate Scale 1:1

## Description

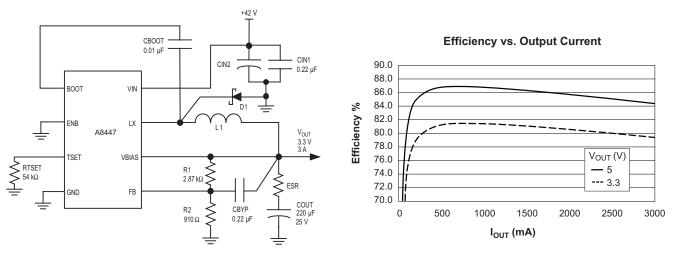

The A8447 is a 3A, high efficiency general-purpose buck regulator designed for a wide variety of applications. The output voltage is adjustable from 0.8 to 24 V, based on a resistor divider and the  $0.8 \text{ V} \pm 3 \%$  reference. External components include an external clamping diode, inductor, and filter capacitor. The off-time is determined by an external resistor to ground. It operates in both continuous and discontinuous modes to maintain light load regulation. An internal blanking circuit is used to filter out transients due to the reverse recovery of the external clamp diode. Typical blanking time is 200 ns.

This new device is ideal for various end products including applications with 8 to 50 V input voltage range and require up to 3 A output current, such as uninterruptible power supplies, point of sale (POS) applications, and industrial applications with 24 or 36 V bus.

Applications include:

- Printer power supplies

- Office automation equipment

- · POS thermal, laser, photo, and inkjet printers

- Tape drives

- Industrial applications

Data is for reference only. Efficiency data from circuit shown in left panel.

#### **Absolute Maximum Ratings**

| Characteristic                      | Symbol               | Conditions | Min. | Тур. | Max. | Units |

|-------------------------------------|----------------------|------------|------|------|------|-------|

| VIN Supply Voltage                  | V <sub>IN</sub>      |            | -    | -    | 50   | V     |

| VBIAS Input Voltage                 | V <sub>BIAS</sub>    |            | -0.3 | _    | 7    | V     |

| SW Switching Voltage                | Vs                   |            | -1   | -    | -    | V     |

| ENB Input Voltage Range             | V <sub>ENB</sub>     |            | -0.3 | _    | 7    | V     |

| Operating Ambient Temperature Range | T <sub>A</sub>       |            | -20  | _    | 85   | °C    |

| Junction Temperature                | T <sub>J</sub> (max) |            | -    | -    | 150  | °C    |

| Storage Temperature                 | T <sub>stg</sub>     |            | -55  | -    | 150  | °C    |

\*Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified current ratings, or a junction temperature, T<sub>J</sub>, of 150°C.

#### Package Thermal Characteristics\*

| Package | R <sub>θJA</sub><br>(°C/W) | РСВ     |  |

|---------|----------------------------|---------|--|

| LJ      | 35                         | 4-layer |  |

\* Additional information is available on the Allegro website.

#### **Ordering Information**

Use the following complete part numbers when ordering:

| Part Number  | Packing                       | Description                                                                                |

|--------------|-------------------------------|--------------------------------------------------------------------------------------------|

| A8447SLJTR-T | 13-in. reel, 3000 pieces/reel | LJ package, SOIC surface mount with exposed thermal pad; leadframe plating 100% matte tin. |

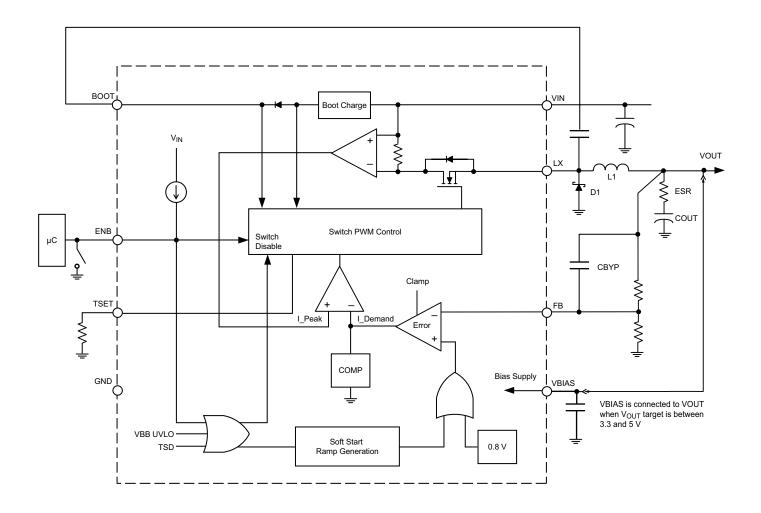

Functional Block Diagram

## ELECTRICAL CHARACTERISTICS<sup>1,2</sup> at $T_A = 25^{\circ}$ C, $V_{IN} = 8$ to 50 V (unless noted otherwise)

| Characteristics                    | Symbol                 | Test Conditions                                                                                           | Min.  | Тур. | Max.  | Units |

|------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

|                                    |                        | $V_{ENB}$ = LOW, I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 42 V,<br>V <sub>BIAS</sub> = V <sub>OUT</sub> | -     | 0.90 | 1.35  | mA    |

| VIN Quiescent Current <sup>3</sup> | I <sub>VIN(Q)</sub>    | $V_{ENB}$ = LOW, I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 42 V,<br>V <sub>BIAS</sub> < 3 V              | -     | 4.4  | 6.35  | mA    |

|                                    |                        | V <sub>ENB</sub> = HIGH                                                                                   | -     | -    | 100   | μA    |

| VBIAS Input Current                | I <sub>BIAS</sub>      | $V_{BIAS} = V_{OUT}$                                                                                      | -     | 3.5  | 5     | mA    |

| Ruck Switch On Desistance          |                        | T <sub>A</sub> = 25°C, I <sub>OUT</sub> = 3 A                                                             | -     | 450  | -     | mΩ    |

| Buck Switch On Resistance          | R <sub>DS(on)</sub>    | T <sub>A</sub> = 125°C, I <sub>OUT</sub> = 3 A                                                            | -     | 650  | -     | mΩ    |

| Fixed Off-Time Proportion          | t <sub>off</sub>       | Based on calculated value                                                                                 | -15   | -    | 15    | %     |

| Feedback Voltage                   | V <sub>FB</sub>        |                                                                                                           | 0.784 | 0.8  | 0.816 | V     |

| Output Voltage Regulation          | V <sub>OUT</sub>       | I <sub>OUT</sub> = 0 mA to 3 A                                                                            | -3    | -    | 3     | %     |

| Feedback Input Bias Current        | I <sub>FB</sub>        |                                                                                                           | -400  | -100 | 100   | nA    |

| Soft Start Time                    | t <sub>ss</sub>        |                                                                                                           | 5     | 10   | 15    | ms    |

|                                    |                        | V <sub>FB</sub> > 0.4 V                                                                                   | 3.5   | -    | 5     | Α     |

| Buck Switch Current Limit          | I <sub>CL</sub>        | V <sub>FB</sub> < 0.4 V                                                                                   | 0.5   | -    | 1.5   | Α     |

| ENB Open Circuit Voltage           | V <sub>oc</sub>        | Output disabled                                                                                           | 2.0   | _    | 7     | V     |

| ENB Input Voltage Threshold        | V <sub>ENB(0)</sub>    | LOW level input (Logic 0), output enabled                                                                 | _     | -    | 1.0   | V     |

| ENB Input Current                  | I <sub>ENB(0)</sub>    | V <sub>ENB</sub> = 0 V                                                                                    | -10   | -    | _1    | μA    |

| VIN Undervoltage Threshold         | V <sub>UVLO</sub>      | V <sub>IN</sub> rising                                                                                    | 6.6   | 6.9  | 7.2   | V     |

| VIN Undervoltage Hysteresis        | V <sub>UVLO(hys)</sub> | V <sub>IN</sub> falling                                                                                   | 0.7   | -    | 1.1   | V     |

| Thermal Shutdown Temperature       | T <sub>JTSD</sub>      | Temperature increasing                                                                                    | -     | 165  | -     | °C    |

| Thermal Shutdown Hysteresis        | T <sub>JTSD(hys)</sub> | Recovery = T <sub>JTSD</sub> – T <sub>JTSD(hys)</sub>                                                     | -     | 15   | -     | °C    |

<sup>1</sup>Negative current is defined as coming out of (sourcing) the specified device pin.

<sup>2</sup>Specifications over the junction temperature range of 0°C to 125°C are assured by design and characterization.

$^3\text{VBIAS}$  is connected to VOUT when the  $\text{V}_{\text{OUT}}$  target is between 3.3 and 5 V.

## **Functional Description**

The A8447 is a fixed off-time, current mode controlled, buck regulator. The regulator requires an external clamping diode, inductor, and filter capacitor. It operates in both continuous and discontinuous modes. An internal blanking circuit is used to filter out transients resulting from the reverse recovery of the external clamp diode. Typical blanking time is 200 ns.

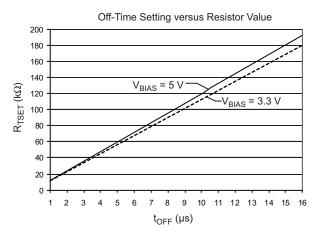

The value of a resistor between the TSET and GND determines the fixed off-time (see graph in the  $t_{OFF}$  section).

$V_{OUT}$ . The output voltage is adjustable from 0.8 to 24 V, set by an external resistor divider. The voltage can be calculated with the following formula:

$$V_{\rm OUT} = V_{\rm FB} \times (1 + R1/R2) \tag{1}$$

**Light Load Regulation.** To maintain voltage regulation during light load conditions, the switching regulator enters a cycle-skipping mode. As the output current decreases, there remains some energy that is stored during the power switch minimum on-time. In order to prevent the output voltage from rising, the regulator skips cycles once it reaches the minimum on-time, effectively making the off-time larger.

**Soft Start.** An internal ramp generator and counter allow the output to slowly ramp up. This limits the maximum demand on the external power supply by controlling the inrush current required to charge the external capacitor and any dc load at startup. Internally, the ramp is set to 10 ms nominal rise time. During soft start, current limit is 3.5 A minimum.

The following conditions are required to trigger a soft start:

- $V_{IN} > 6 V$

- ENB pin input falling edge

- Reset of a TSD (thermal shut down) event

$V_{BIAS}$ . To improve overall system efficiency, the regulator output,  $V_{OUT}$ , is connected to the VBIAS input to supply the operating bias current during normal operating conditions. During startup the circuitry is run off of the VIN supply. VBIAS should be connected to VOUT when the  $V_{OUT}$  target level is between 3.3 and 5 V. If the output voltage is less than 3.3 V, then the A8447 can operate with an internal supply and pay a penalty in efficiency, as the bias current will come from the high voltage source. No power-up sequencing is required for normal operation.

**ON/OFF Control.** The ENB pin is externally pulled to ground to enable the device and begin the soft start sequence. When the ENB is open circuited, the switcher is disabled and the output decays to 0 V.

**Protection.** The buck switch will be disabled under one or more of the following fault conditions:

- $V_{IN} < 6 V$

- ENB pin = open circuit

- TSD fault

When the device comes out of a TSD fault, it will go into a soft start to limit inrush current.

$t_{OFF}$ . The value of a resistor between the TSET pin and ground determines the fixed off-time. The formula to calculate  $t_{OFF}$  (µs) is:

$$t_{\rm OFF} = R_{\rm TSET} \left( \frac{1 - 0.03 \times V_{\rm BIAS}}{10.2 \times 10^9} \right),$$

(2)

where  $R_{TSET}(k\Omega)$  is the value of the resistor. Results are shown in the following graph:

**Shorted Load.** If the voltage on the FB pin falls below 0.4 V, the regulator will invoke a 1.5 A typical overcurrent limit to handle the shorted load condition at the regulator output. For low output voltages at power up and in the case of a shorted output, the off-time is extended to prevent loss of control of the current limit due to the minimum on-time of the switcher.

The extension of the off-time is based on the value of the TSET multiplier and the FB voltage, as shown in the following table:

| V <sub>FB</sub> (V) | TSET Multiplier      |

|---------------------|----------------------|

| < 0.16              | 8 × t <sub>OFF</sub> |

| < 0.32              | $4 \times t_{OFF}$   |

| < 0.5               | 2 × t <sub>OFF</sub> |

| > 0.5               | t <sub>OFF</sub>     |

### **Component Selection**

**L1.** The inductor must be rated to handle the total load current. The value should be chosen to keep the ripple current to a reasonable value. The ripple current,  $I_{RIPPLE}$ , can be calculated by:

$$I_{\text{RIPPLE}} = V_{\text{L(OFF)}} \times t_{\text{OFF}} / L$$

(3)

$$V_{L(OFF)} = V_{OUT} + V_f + I_{L(AV)} \times R_L$$

(4)

Example:

Given  $V_{OUT} = 5 \text{ V}$ ,  $V_f = 0.55 \text{ V}$ ,  $V_{IN} = 42 \text{ V}$ ,  $I_{LOAD} = 0.5 \text{ A}$ , power inductor with L = 180  $\mu$ H and  $R_L = 0.5 \Omega$  Rdc at 55°C,  $t_{OFF} = 7 \mu$ s, and  $R_{DS(on)} = 1 \Omega$ .

Substituting into equation 6:

$$V_{L(OFF)} = 5 V + 0.55 V + 0.5 A \times 0.5 \Omega = 5.8 V$$

Substituting into equation 5:

$$I_{RIPPLE} = 5.8 \text{ V} \times 7 \ \mu \text{s} / 180 \ \mu \text{H} = 225 \text{ mA}$$

The switching frequency,  $f_{SW}$ , can then be estimated by:

$$f_{\rm SW} = 1 / (t_{\rm ON} + t_{\rm OFF})$$

(5)

$$t_{\rm ON} = I_{\rm RIPPLE} \times L / V_{\rm L(ON)}$$

(6)

$$V_{L(ON)} = V_{IN} - I_{L(AV)} \times R_{DS(on)} - I_{L(AV)} \times R_{L} - V_{OUT}$$

(7)

Substituting into equation 9:

$$V_{L(ON)} = 42 \text{ V} - 0.5 \text{ A} \times 1 \Omega - 0.5 \text{ A} \times 0.5 \Omega - 5 \text{ V} = 36 \text{ V}$$

Substituting into equation 8:

$$t_{ON}$$

= 225 mA × 180  $\mu$ H / 36 V = 1.12  $\mu$ s

Substituting into equation 7:

$$f_{SW} = 1 / (7 \ \mu s + 1.12 \ \mu s) = 123 \ kHz$$

Higher inductor values can be chosen to lower the ripple current. This may be an option if it is required to increase the total maximum current available above that drawn from the switching regulator. The maximum total current available,  $I_{\text{LOAD}(\text{MAX})}$ , is:

$$I_{\text{LOAD(MAX)}} = I_{\text{CL}}(\min) - I_{\text{RIPPLE}} / 2$$

(8)

where I<sub>CL</sub>(min) is 3.5 A, from the Electrical Characteristics table.

**D1.** The Schottky catch diode should be rated to handle 1.2 times the maximum load current. The voltage rating should be higher than the maximum input voltage expected during all operating conditions. The duty cycle for high input voltages can be very close to 100%.

**COUT.** The main consideration in selecting an output capacitor is voltage ripple on the output. For electrolytic output capacitors, a low-ESR type is recommended.

The peak-to-peak output voltage ripple is simply  $I_{RIPPLE} \times ESR$ . Note that increasing the inductor value can decrease the ripple current. The minimum voltage rating of the capacitor is 10 V. However, because ESR decreases with voltage, the most cost-effective choice may be rated higher in voltage. It is recommended that the ESR be less than 100 m $\Omega$ .

**RTSET Selection.** Correct selection of RTSET values will ensure that minimum on time of the switcher is not violated and prevent the switcher from cycle skipping. For a given  $V_{IN}$ to  $V_{OUT}$  ratio,  $R_{TSET}$  must be greater than or equal to the value defined by the curve in the RTEST Value Selection graph below.

Note. The curve represents the minimum RTSET value. When calculating  $R_{TSET}$ , be sure to use  $V_{IN}(max) / V_{OUT}(min)$ . Resistor tolerance should also be considered, so that under all operating

#### **RTSET Value Selection**

conditions the resistance on the TSET pin remains as close to the curve as possible.

The RTEST Selection table shows recommended  $R_{TSET}$  values based on common operating conditions. For other operating conditions, refer to the RTSET Value Selection graph.

**FB Resistor Selection.** The impedance of the FB network should be kept low to improve noise immunity. Large value resistors can pick up noise generated by the inductor, which can affect voltage regulation of the switcher.

| Selection Graph                                     | Recommended Common Values |                         |                                   |                                 |  |

|-----------------------------------------------------|---------------------------|-------------------------|-----------------------------------|---------------------------------|--|

| 70                                                  | V <sub>IN</sub><br>(V)    | V <sub>OUT</sub><br>(V) | V <sub>IN</sub> /V <sub>OUT</sub> | R <sub>TSET</sub> Value<br>(kΩ) |  |

| 60                                                  | 42                        | 5                       | 8.4                               | 37.4                            |  |

| 55 50                                               | 42                        | 3.3                     | 12.7                              | 54.9                            |  |

| 45<br>40<br>35                                      | 42                        | 1.8                     | 23.3                              | 90.9                            |  |

| 2 35<br>¥ 30                                        | 24                        | 5                       | 4.8                               | 20.0                            |  |

| 25                                                  | 24                        | 3.3                     | 7.3                               | 32.4                            |  |

| 15                                                  | 24                        | 1.8                     | 13.3                              | 54.9                            |  |

| 10<br>5                                             | 12                        | 5                       | 2.4                               | 7.68                            |  |

| 0 15 30 45 60 75 90 105 120 135 150 165 180 195 210 | 12                        | 3.3                     | 3.6                               | 13.7                            |  |

| R <sub>TSET</sub> (kΩ)                              | 12                        | 1.8                     | 6.6                               | 30.1                            |  |

#### **Recommended Components**

| Component                                | Descr                                                | Part Number       |                  |  |

|------------------------------------------|------------------------------------------------------|-------------------|------------------|--|

| L1                                       | Sumida 68 µH                                         | RCH1216BNP-680K   |                  |  |

| D1                                       | NIEC Schottky Barrier Die                            | ode 60 V TO-252AA | NSQ03A06         |  |

| СВҮР                                     | Ceramic X7A 0.22 µF 100                              | D V               | Generic          |  |

| СВООТ                                    | Ceramic X7A 0.01 µF 100                              | 0 V               | Generic          |  |

| CIN                                      | Electrolytic 100 µF 50 V<br>worst case ripple curent | Generic           |                  |  |

|                                          | Ceramic X7A 0.22 µF 50                               | Generic           |                  |  |

| United Chemi-Con PXA 220 µF 16 V Low ESR |                                                      |                   | PXA16VC221MJ12TP |  |

| COUT                                     | COUT Rubycon ZL 220 µF 25 V Low ESR (Option 1)       |                   | 25ZL220M8x11.5   |  |

|                                          | Panasonic FM 220 µF 25 V Low ESR (Option 2)          |                   | EEUFM1E221       |  |

|                                          | V <sub>OUT</sub>                                     |                   |                  |  |

|                                          | 1.8 V                                                | 3.3 V             | 5 V              |  |

| R1                                       | 2.55 kΩ                                              | 2.87 kΩ           | 6.3 kΩ           |  |

| R2                                       | 2 kΩ                                                 | 0.910 kΩ          | 1.2 kΩ           |  |

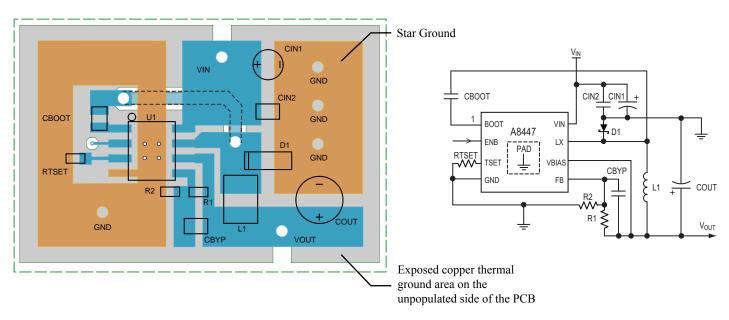

## Recommended PCB Layout

In order to minimize the effects of ground bounce and offset issues, it is important to have a low impedance ground located very close to the device. This grounding scheme is known as star grounding. It is likely that a ground plane will be necessary to meet thermal requirements. The recommended land pattern illustrates how to create a low impedance ground that will also assist with removing thermal energy from the device.

The input capacitor must be placed as close as possible to the VIN terminal because during the on cycle it is responsible for supplying the current to the switcher. During the off cycle, the current path is from the negative terminal of the COUT cap, through the diode and inductor, and then to the load. As a result, COUT and the rectifier diode must share the connection at the negative terminal of the CIN capacitor in order to reduce ground bounce when the diode is conducting. The inductor should be connected as close as possible to the switching node to minimize noise. Some applications may require a shielded inductor due to EMI restrictions. This will depend on the application and parameters defined by the system that will host the regulator.

The high voltage-switching node could affect  $R_{TSET}$ . If longer off-times are used, the resistance on the RTSET pin can be quite large. When designing the layout, try to keep RTSET away from the inductor and switching node. It is also beneficial to keep the trace as short as possible to reduce the effect of noise injection. Because of this layout guideline, the TSET pin is located on the other side of the device, away from the switching node.

The FB resistor network should have a lower impedance to avoid interference from the switching node. Because the impedance on the FB node can be controlled, it is not as critical to keep the network isolated. It is important to keep the ground trace short so that ground bounce cannot effect the output voltage regulation.

The large star ground area on the populated side of the PCB, shown in the diagram as the GND nodes, supports high current throughput, and allows the VOUT node to be located as close as practical to the A8447 (U1). Thermal conduction from the A8447 is enhanced by direct contact of its exposed thermal pad to the smaller ground area under the A8447. This area is connected by thermal vias to the large copper ground plane on the unpopulated side of the PCB.

Package LJ 8 Pin SOIC

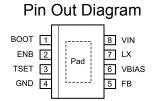

#### **Terminal List Table**

| Number | Name  | Description                       |

|--------|-------|-----------------------------------|

| 1      | BOOT  | Gate drive boost node             |

| 2      | ENB   | On/off control; logic input       |

| 3      | TSET  | Off-time setting                  |

| 4      | GND   | Ground                            |

| 5      | FB    | Feedback for adjustable regulator |

| 6      | VBIAS | Bias supply input                 |

| 7      | LX    | Buck switching node               |

| 8      | VIN   | Supply input                      |

The products described herein are manufactured under one or more patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support appliances, devices, or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties that may result from its use.

Copyright © 2006 Allegro MicroSystems, Inc.